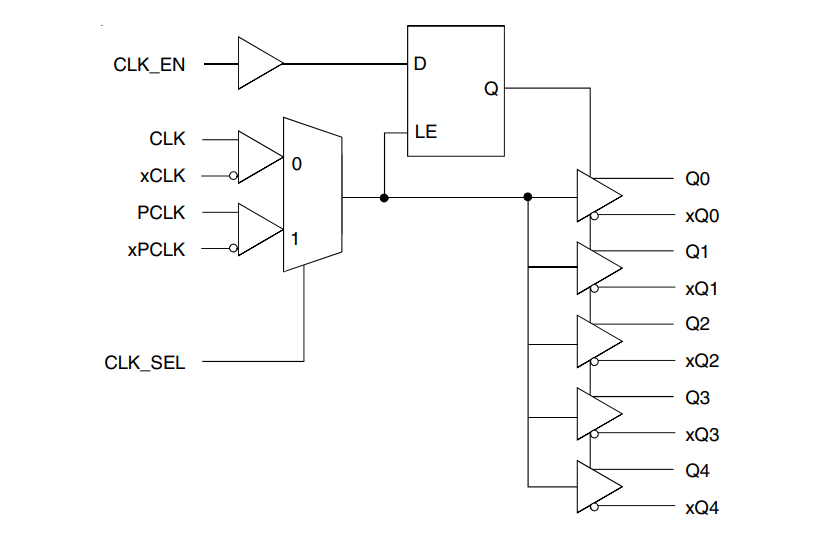

The IDT85304-01 is a low-tilt, high-performance 1-to-5 difference-to-3.3V LVPECL clock generator - voltage divider. It has two optional clock inputs. CLK/ xCLK pairs can accept most standard differential input levels.

Schematic diagram

PCLK/ xPCLK pairs can accept LVPECL, CML, or SSTL input levels. Clock enablement is internally synchronized to eliminate small pulses on the output during asynchronous assertion/undo assertion of the clock enablement pin. The guaranteed output and partial to partial tilt characteristics make the IDT85304-01 ideal for those applications requiring good performance and repeatability

Sequence diagram

Product features:

• 5 Differential 3.3V LVPECL output

• Optional differential CLK, xCLK, or LVPECL clock input

• CLK and xCLK pairs accept the following differential input levels:LVDS, lvvpecl, LVHSTL, SSTL and HCSL

• PCLK, xPCLK supports the following input types :LVPECL, CML,And Surrey

• Maximum output frequency 650MHz

• Convert any single-ended input signal to a 3.3V LVPECL level the xCLK input resistance is offset

• Output tilt :35ps(Max)

• Partial to partial skew: As low as 150ps

• Propagation delay :2.1ns(Max)

• 3.3V power supply

• Available in TSSOP packaging